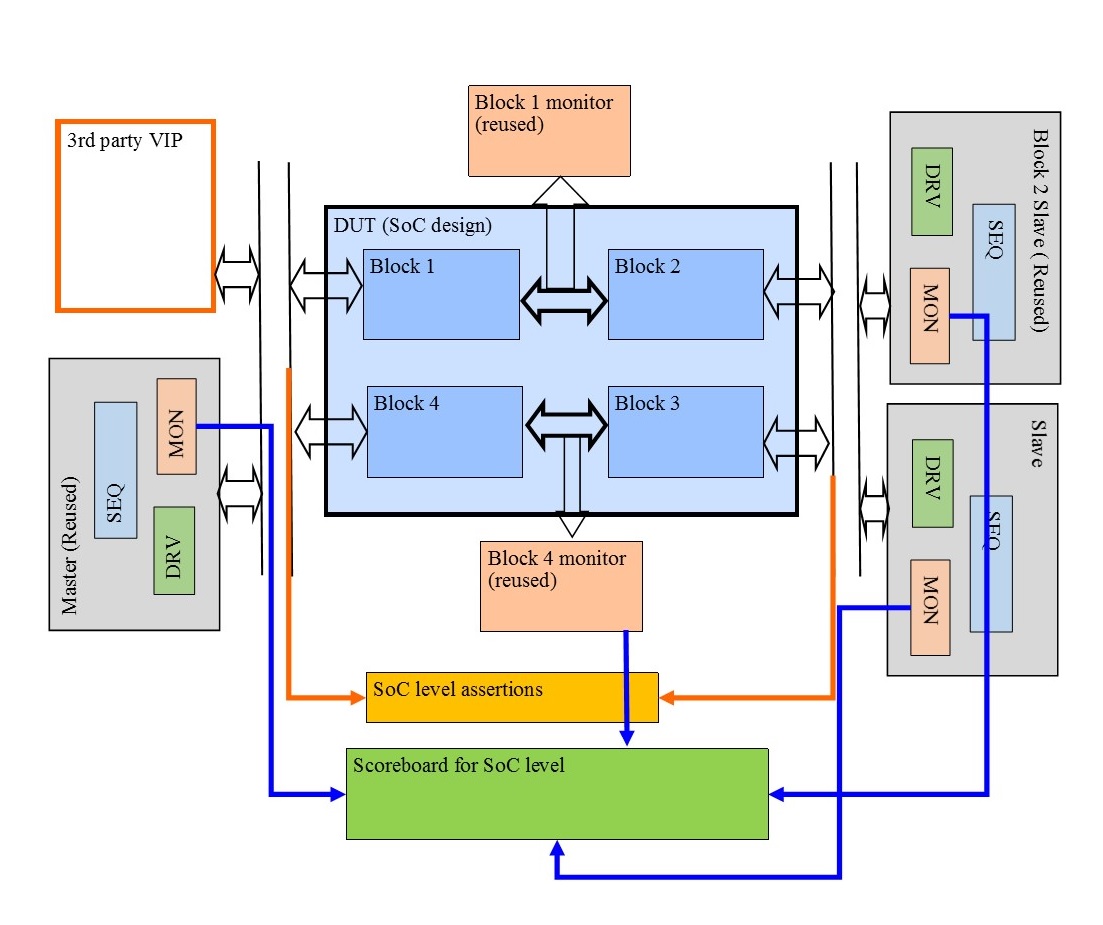

Above block diagram shows a

typical system level testbench architecture reusing UVCs and using

third party VIP

A

System on Chip (SoC) will constitute many design blocks working in

sync to accomplish a final function or operation. Full chip

verification of a design will need well defined requirements at

top/ chip level as well as at constituent block level. All

constituent blocks of a chip will be verified first using a block

level testbench and a seperate top system verification environment

will be created for full chip level verification. System level

verification environment may reuse some block level verification

components.

Highlights of Verification Technique

Please click here to know more about this service.